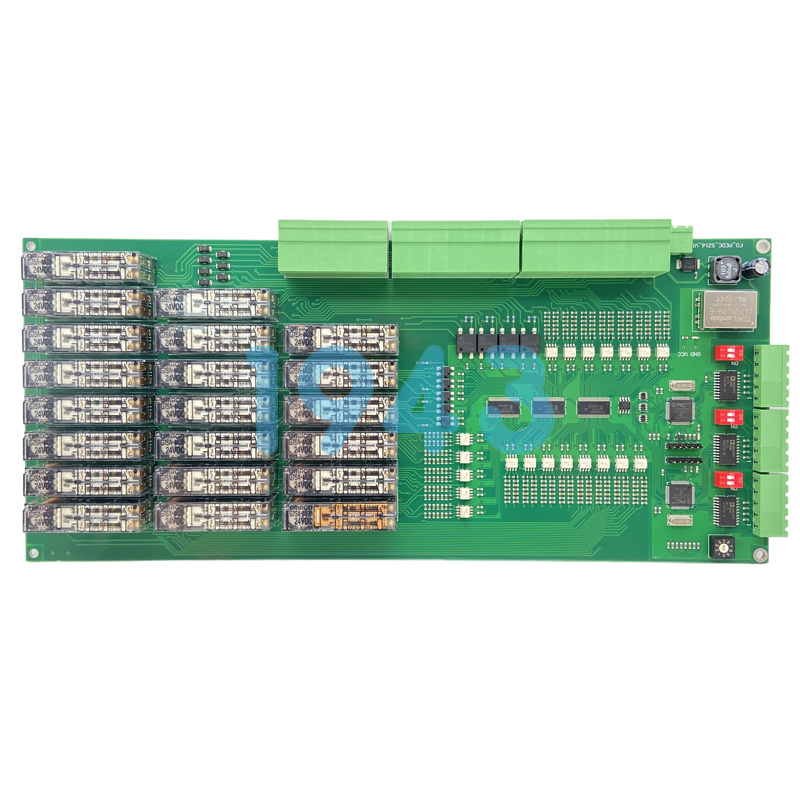

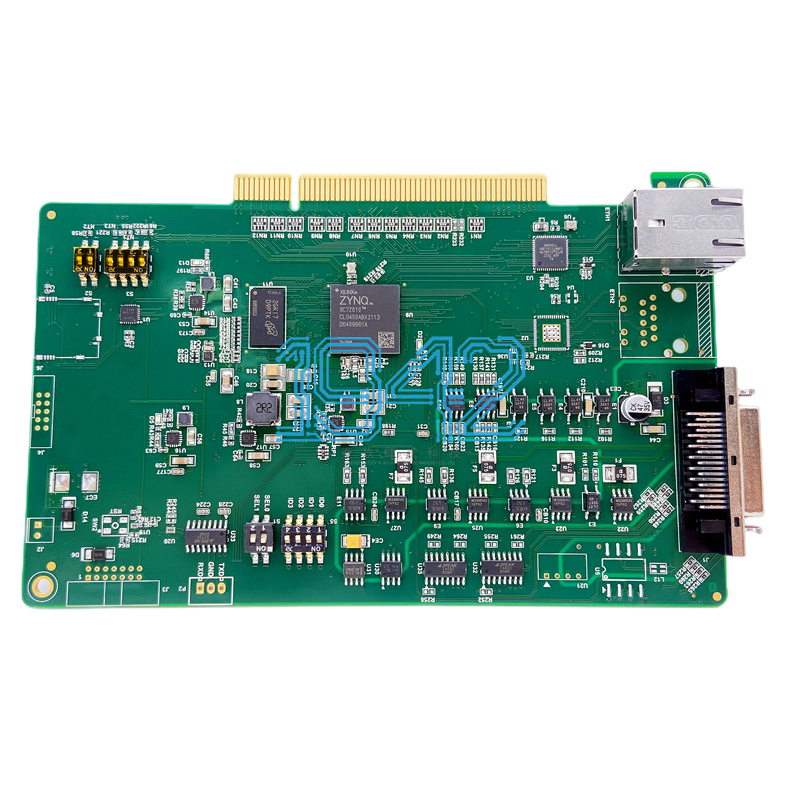

在電子制造領(lǐng)域,電磁兼容性(EMC)是衡量PCBA產(chǎn)品性能與穩(wěn)定性的核心指標(biāo)。隨著高頻、高密度電路設(shè)計的普及,SMT貼片工藝中的EMC問題已成為影響設(shè)備可靠性的關(guān)鍵挑戰(zhàn)。1943科技從設(shè)計、工藝、材料三大維度,深入探討如何通過系統(tǒng)性優(yōu)化提升PCBA的電磁兼容性,助力企業(yè)打造高性能、高可靠性的電子產(chǎn)品。

一、EMC問題的根源與影響?

在SMT貼片加工中,電磁干擾(EMI)主要源于高頻信號傳輸、大電流回路及元件布局不合理。若未有效抑制EMI,可能導(dǎo)致以下問題:

- 信號失真:高頻信號因電磁耦合產(chǎn)生反射或衰減,影響數(shù)據(jù)傳輸精度。

- 系統(tǒng)穩(wěn)定性下降:敏感電路(如控制單元)受干擾后易引發(fā)誤動作或數(shù)據(jù)丟失。

- 認(rèn)證不達(dá)標(biāo):電磁輻射超標(biāo)將無法通過IEC 61000等國際標(biāo)準(zhǔn)認(rèn)證,阻礙產(chǎn)品上市。

二、SMT貼片工藝中的EMC優(yōu)化策略?

1. 設(shè)計階段的EMC布局優(yōu)化?

- 分區(qū)布局:嚴(yán)格劃分模擬電路、數(shù)字電路及電源模塊區(qū)域,避免交叉干擾。例如,將大電流回路與敏感信號線分離,并通過地平面隔離。

- 關(guān)鍵元件配置:

- 去耦電容:在IC電源引腳附近配置0.01μF~0.1μF陶瓷電容,高頻旁路電容需靠近芯片。

- 地線設(shè)計:采用多層PCB結(jié)構(gòu),設(shè)置≥2mm寬的地平面,減少接地阻抗。數(shù)字地與模擬地通過單點連接,避免環(huán)路干擾。

2. 布線策略與信號完整性?

- 減少環(huán)路面積:信號線與回流路徑保持平行,縮短環(huán)路長度,抑制環(huán)形天線效應(yīng)。

- 差分信號處理:對USB、LVDS等高速差分信號采用對稱布線,利用共模抵消特性降低干擾。

- 避免直角走線:信號線拐角采用135°斜角或圓弧形,減少高頻反射。

3. 工藝優(yōu)化與屏蔽技術(shù)?

- SMT貼片精度:確保元件引腳與焊盤完全對齊,降低接觸電阻與寄生電感。

- 屏蔽層集成:在PCB多層結(jié)構(gòu)中嵌入銅箔或?qū)щ娔z屏蔽層,并與地平面連接,形成電磁屏障。

- 濾波器應(yīng)用:在電源輸入端及信號接口集成共模扼流圈、鐵氧體磁珠等EMI濾波器,抑制高頻噪聲。

三、材料選擇與結(jié)構(gòu)設(shè)計?

- 低介電常數(shù)基材:選用FR4等低損耗材料,減少高頻信號輻射損耗。

- 通孔絕緣膠技術(shù):通過填充絕緣膠形成物理隔離層,阻斷電磁輻射路徑。

- 散熱與EMC協(xié)同設(shè)計:合理規(guī)劃散熱孔與風(fēng)道,避免局部高溫導(dǎo)致元件參數(shù)漂移,進(jìn)而引發(fā)EMI問題。

四、全流程協(xié)同與測試驗證?

- 設(shè)計-工藝協(xié)同:在PCB設(shè)計階段即考慮SMT貼片工藝能力,避免因貼裝偏差導(dǎo)致地平面斷裂或屏蔽失效。

- 自動化檢測:引入AOI(自動光學(xué)檢測)與X射線設(shè)備,實時監(jiān)控焊接質(zhì)量與元件貼裝精度。

- EMC測試閉環(huán):通過頻譜分析儀、近場探頭等工具定位干擾源,迭代優(yōu)化設(shè)計方案。

五、結(jié)語?

提升PCBA的電磁兼容性需貫穿設(shè)計、工藝、材料全鏈條。通過科學(xué)布局、高精度貼片及屏蔽技術(shù),可顯著降低EMI風(fēng)險,助力產(chǎn)品通過嚴(yán)苛認(rèn)證。1943科技深耕SMT貼片加工領(lǐng)域,以技術(shù)創(chuàng)新為驅(qū)動,為企業(yè)提供從設(shè)計支持到量產(chǎn)交付的一站式解決方案。 立即聯(lián)系1943科技,獲取定制化SMT貼片加工EMC優(yōu)化方案,賦能您的產(chǎn)品搶占市場先機(jī)!

2024-04-26

2024-04-26